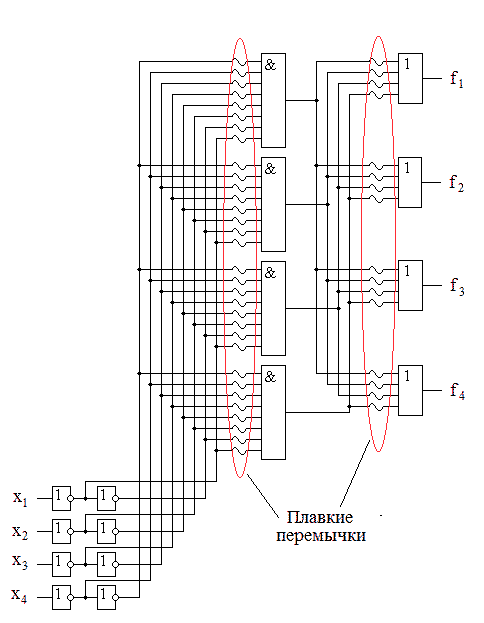

Первым представителем большого класса программируемых логических устройств (ПЛИС) стали программируемые логические матрицы (ПЛМ). В зарубежной литературе они называются PLA — Programmable logic Array. Обобщенная структура ПЛМ приведена на рисунке 1.

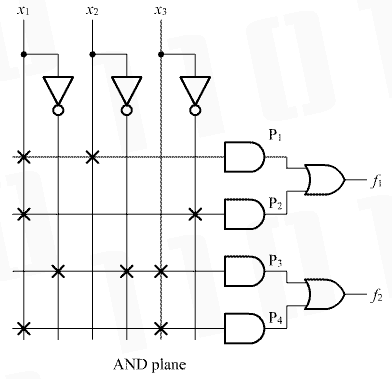

Основная идея работы ПЛМ заключается в реализации логической функции, представленной в СДНФ — дизъюнктивной нормальной форме. На рисунке четко прослеживаются логические элементы "И", способные реализовать любой минтерм СДНФ и логические элементы "ИЛИ", осуществляющие суммирование термов, требующихся по логическому выражению СДНФ. В схеме ПЛМ, приведенной на рисунке 1, ранг терма ограничен количеством входов и равен четырем, количество термов тоже равно четырем. В реально выпускавшихся микросхемах программируемых логических матриц (ПЛМ) количество входов было равно шестнадцати (максимальный ранг минтерма — 16), количество термов равно 32 и количество выходов микросхемы — 8.

Примерами реализации программируемых логических матриц могут служить отечественные микросхемы K556PT1, PT2, PT21. В этих микросхемах программирование осуществлялось при повышенном напряжении питания. Там, где требовалось сохранить плавкую перемычку на ее вход и выход подавалось высокое напряжение, там, где соединение не требовалось, на вход подавался потенциал корпуса (логический ноль), а на выход — напряжение питания. Перемычка из поликристаллического кремния под воздействием высокой температуры, вызванной током короткого замыкания, испарялась.

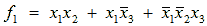

Следует отметить, что полная принципиальная схема ПЛМ получается достаточно громоздкой (см. рисунок 1). Поэтому в зарубежной литературе обычно применяется шинное представление проводников. Логический элемент "И", реализующий минтерм СДНФ, изображается как одиночная горизонтальная строка с условно-графическим обозначением схемы "И". Ко входам этого элемента подводится многоразрядная шина, а на выходе подключен одиночный проводник. Если входной проводник подключается ко входу логического элемента "И" (перемычка сохранена), то это место обозначается крестиком 'x', а если соединение отсутствует (перемычка сожжена), то крестик не проставляется. Аналогично обозначаются и многовходовые элементы "ИЛИ". Пример подобного изображения схемы ПЛМ (PLA) приведен на рисунке 2.

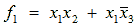

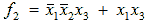

По схеме четко можно восстановить реализуемую им логическую функцию. На рисунке 2 реализованы две логические функции f1 и f2:

Недостаток рассмотренной архитектуры ПЛМ — слабое использование ресурсов программируемой матрицы логических элементов "ИЛИ". Данное обстоятельство привело к появлению ещё одного вида ПЛМ — PAL.

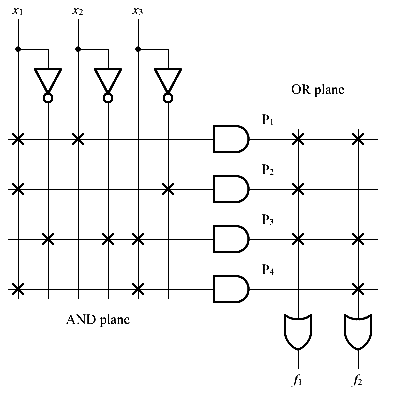

В программируемой логической матрице (ПЛМ) обе матрицы логических элементов "И" и "ИЛИ" программируемы. ПЛИС, в которых матрица логических элементов "И" являетсяпрограммируемой, а матрица логических элементов "ИЛИ" фиксированной, получили название программируемых матриц логики ПМЛ или PAL — Programmable Array Logic (англ.). Поскольку изготовить такие устройства проще, чем ПЛМ, они имеют меньшую стоимость и обладают улучшенными характеристиками, что привело к их высокой популярности. Пример ПМЛ с тремя входами, четырьмя логическими элементами "4ИЛИ", реализующими четыре минтерма шестого ранга и двумя выходами представлен на рисунке 3.

Напомню, что в схеме, приведенной на рисунке 1, действует следующее соглашение: Количество входов у логических элементов "И" равно количеству проводников на входе схемы (в данном случае шесть). Соединения, помеченные крестиком подключены ко входам логического элемента, остальные входы логического элемента "И" подключены через резистор к источнику питания, а значит не влияют на результат работы. Представленные на рисунке 1 запрограммированные соединения реализуют следующие логические функции:

Логическиеэлементы "4И", реализующие термы P1 и P2 аппаратно соединены с первым элементом ИЛИ, а логические элементы "4И", реализующие термы P3 и P4 аппаратно соединены со вторым элементом. Эти соединения не могут программироваться. По сравнению с ПЛМ, программируемые матрицы логики обладает меньшей гибкостью программирования. ПМЛ позволяет использовать четыре терма в качестве входов для элементов ИЛИ, а элементы ИЛИ в ПМЛ имеют только два фиксированных входа. Для компенсации этого недостатка производители ПМЛ производят микросхемы разного объема с различным числом входов и выходов, а также различным числом входов логических элементов "ИЛИ".

К программируемым матрицам логики относятся большинство современных ПЛИС небольшой степени интеграции. В качестве примера подобных микросхем можно привести отечественные ИС КМ1556ХП4, КМ1556ХП6, КМ1556ХП8, КМ1556ХЛ8, ранние разработки микросхем ПЛИС (середина-конец 1980-х годов) фирм INTEL, ALTERA, AMD, LATTICE и др. Разновидностью этого класса микросхем являются ПЛИС, имеющие только одну (программируемую) матрицу логических элементов "И", например, микросхема 85C508 фирмы INTEL. Следующий традиционный тип ПЛИС — программируемая макрологика. Подобные микросхемы содержат единственную программируемую матрицу "И-НЕ" или "ИЛИ-НЕ", но за счёт многочисленных инверсных обратных связей способны формировать сложные логические функции. К этому классу относятся, например,ПЛИС PLHS501 и PLHS502 фирмы SIGNETICS, имеющие матрицу "И-НЕ", а также схема XL78C800 фирмы EXEL, реализованная на матрице логических элементов "ИЛИ-НЕ"